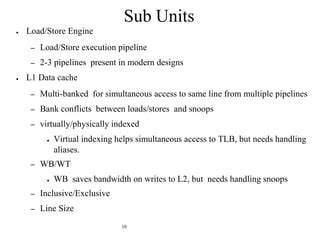

En el vasto mundo de la informática, la optimización del rendimiento es un objetivo constante para desarrolladores y arquitectos de hardware. Entre los múltiples factores que influyen en la eficiencia de ejecución de los programas, los conflictos entre operaciones de carga (load) y almacenamiento (store) en el procesador representan un desafío técnico significativo. Estos conflictos, poco visibles para el desarrollador promedio, pueden desencadenar importantes cuellos de botella en códigos sensibles a la latencia y al ancho de banda de memoria, afectando especialmente a los algoritmos críticos en tiempo real y procesamiento en alta velocidad. La interacción entre instrucciones de carga y almacenamiento se lleva a cabo a través de estructuras internas del procesador conocidas como buffers de tienda o store buffers. En esencia, cuando un procesador debe almacenar un dato, en lugar de realizar una escritura inmediata en el caché L1 o en la memoria principal, la información se mantiene primero en este buffer temporal.

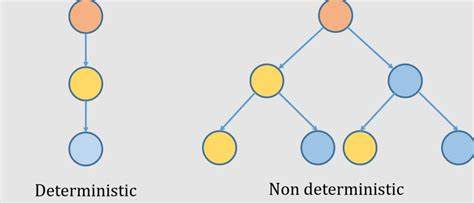

Esto permite que el procesador continúe ejecutando instrucciones siguientes sin esperar a que la operación de escritura se complete realmente. Sin embargo, cuando una instrucción de carga intenta acceder a una dirección que tiene una escritura pendiente en el buffer de tienda, surge la necesidad de una reconciliación eficiente entre ambas operaciones para evitar errores y garantizar coherencia. El proceso conocido como store-to-load forwarding es el método mediante el cual el procesador puede satisfacer una carga con los datos que aún no han sido escritos definitivamente en el caché, extrayéndolos directamente desde el buffer de tienda. De esta manera, se reducen los tiempos de espera y se evita que el rendimiento languidezca ante el constante ir y venir de datos. No obstante, la implementación de este mecanismo varía entre diferentes arquitecturas y generaciones de CPUs, y su eficacia depende en gran medida de cómo esté escrito y compilado el código.

Un caso particular y revelador de este fenómeno es el análisis realizado sobre un decodificador de índices presente en la biblioteca meshoptimizer, que se utiliza para descomprimir datos geométricos a alta velocidad. Este decodificador maneja un buffer FIFO de bordes representados por pares de índices de 32 bits y realiza frecuentes accesos de lectura y escritura en este buffer dentro de un ciclo crítico. El rendimiento de esta operación impacta directamente la velocidad de procesamiento de varios gigabytes por segundo. Las pruebas realizadas con diferentes compiladores y versiones demuestran cómo pequeños cambios en la generación de código pueden suponer diferencias notables en el rendimiento. Por ejemplo, la generación de código con Clang 20 en una arquitectura x86_64 produce instrucciones sencillas que manejan los datos de a 32 bits, leyendo y escribiendo los valores por separado.

Esta estrategia funciona razonablemente bien, alcanzando decodificaciones alrededor de 6.6 GB/s en procesadores Ryzen 7950X. Por otra parte, GCC versión 14 introduce una técnica más sofisticada al utilizar instrucciones vectoriales SSE que permiten manejar los pares de índices como un solo dato de 64 bits. Esta forma de operar reduce el número de instrucciones de escritura y permite mayor paralelismo en la ejecución, mejorando el rendimiento hasta alcanzar aproximadamente 7.5 GB/s, una mejora superior al 10 % respecto a Clang 20.

Sin embargo, el escenario cambia drásticamente con la llegada de GCC 15. En esta versión, el compilador cambia la forma de generar el código y, aunque parece simplificar el proceso evitando algunas cargas redundantes, termina produciendo un código que genera conflictos entre las operaciones de carga y almacenamiento en el buffer FIFO. Específicamente, la carga de un valor de 64 bits busca datos que provienen de dos escrituras separadas de 32 bits anteriores aún en el buffer de tienda, situación que el procesador no puede gestionar eficientemente. Este conflicto, identificado como una falla en la canalización de la transferencia store-to-load (STLI o store-to-load interlock), genera retrasos importantes en la ejecución del ciclo crítico, incrementando los ciclos por iteración y reduciendo el rendimiento hasta valores inferiores a 5 GB/s. La importancia de detectar y evitar estos conflictos reside en que, aunque el código fuente y la lógica del algoritmo no han cambiado, las decisiones del compilador sobre cómo agrupar o separar las operaciones pueden producir impactos drásticos en el tiempo de procesamiento.

Analizar estos casos también hace evidente cómo las particularidades de la arquitectura del procesador afectan el comportamiento. Mientras procesadores basados en Zen 4 de AMD sufren severamente con los conflictos STLI generados por GCC 15, el rendimiento en Apple Silicon, como en el Apple M4, es diferente gracias a características avanzadas de su microarquitectura que permiten cierta flexibilidad en cómo se puede realizar el store-to-load forwarding. Por ejemplo, las instrucciones de carga y almacenamiento pareadas en ARMv8 utilizadas por Clang 17 en Apple proporcionan una forma más eficiente de manejar datos simultáneos evitando el fenómeno de conflicto que se observa en x86_64. Este comportamiento destaca la importancia de entender no solo el algoritmo a un nivel abstracto, sino también de conocer cómo las instrucciones se traducen a nivel de hardware y qué características específicas ofrece la CPU objetivo. En procesos de ingeniería de software de alto rendimiento, es frecuente que pequeños ajustes en la comunidad de compiladores, o la selección de diferentes flags de compilación, puedan resolver problemas de rendimiento aparentemente inexplicables.

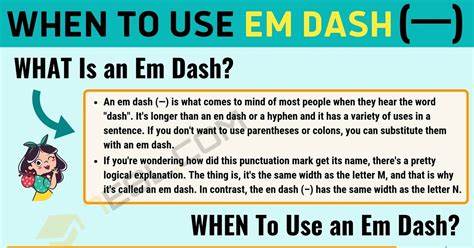

Los desarrolladores también deben estar alertas a los posibles efectos secundarios provocados por la combinación de instrucciones a nivel de código máquina. Por ejemplo, ciertas estructuras de datos o patrones de acceso que generan escrituras o lecturas fragmentadas pueden ser problemáticos si no se agrupan adecuadamente, aumentando el riesgo de divisiones no óptimas de datos en el buffer de tienda. Esto puede ser más relevante en sistemas que manejan valores no alineados o tipos de datos con tamaños irregulares. Por otra parte, hay implicaciones prácticas relevantes para el campo del desarrollo multiplataforma. Variaciones en las optimizaciones de compiladores tan populares como Clang y GCC, sumadas a diferencias arquitectónicas entre x86 y ARM, obligan a la creación de estrategias específicas para cada entorno o equipo de destino.

No es raro que código optimizado para un sistema particular requiera ajustes no triviales para mantener un nivel de rendimiento comparable en otra plataforma. En suma, los conflictos de carga y almacenamiento, especialmente aquellos derivados de la falta o ineficiencia en los mecanismos de store-to-load forwarding, son un fenómeno crítico que influye en el rendimiento del software. Comprender cómo son generados por el compilador, cómo el procesador los maneja y qué señales de diagnóstico se pueden aprovechar para identificarlos, provee a los ingenieros de herramientas precisas para optimizar código sensible de alto rendimiento. Revisar inspecciones detalladas del código ensamblador generado y usar herramientas de perfilado capaces de detectar eventos específi cos, como las fallas de store-to-load, es fundamental para decidir qué cambios en el código fuente o en parámetros de compilación resultan efectivos. El entorno de desarrollo moderno ofrece cada vez más soporte para estas tareas, facilitando la detección precoz de problemas y favoreciendo la producción de software eficiente y estable en variadas condiciones.