En la última década, los modelos de lenguaje a gran escala (LLM) han transformado profundamente la inteligencia artificial, facilitando aplicaciones desde chatbots avanzados hasta sistemas de traducción automática y generación de contenidos. Sin embargo, estos modelos, aunque poderosos, enfrentan considerables desafíos en cuanto a velocidad y consumo energético durante el proceso de inferencia, especialmente cuando se trata de dispositivos de consumo que buscan ejecutar estas tareas de manera eficiente y en tiempo real. La multiplicación matriz-vector (GeMV), fundamental en la operación de estos modelos, se presenta como uno de los cuellos de botella más críticos debido a su alta demanda computacional y de memoria. Tradicionalmente, la ejecución de GeMV se realiza en la unidad central o en procesadores especializados, lo que limita la velocidad y eleva el consumo energético. No obstante, recientes avances apuntan a una solución innovadora que reutiliza la memoria DRAM estándar, sin modificaciones, para acelerar esta operación a niveles sin precedentes, beneficiando especialmente a los modelos de bajo bit cuantificados.

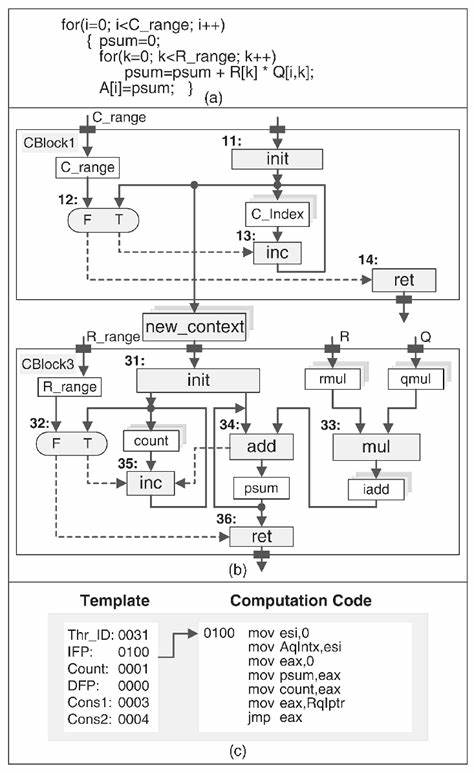

La técnica de Cómputo Dentro de la DRAM (PUD, por sus siglas en inglés) emerge como una estrategia revolucionaria para abordar estos retos. La premisa fundamental detrás de PUD es transformar la memoria DRAM, tradicionalmente un simple almacenamiento, en un motor de cómputo analógico capaz de ejecutar operaciones matemáticas complejas, como la multiplicación matriz-vector, directamente en el hardware donde residen los datos. Esto elimina la necesidad de movimientos continuos de datos entre la memoria y el procesador, reduciendo así la latencia y la energía consumida en la transferencia. Sin embargo, la aplicación práctica de PUD en operaciones GeMV para modelos LLM ha sido limitada debido a los elevados costos en las etapas previas y posteriores al cómputo dentro de la DRAM, que incluyen la preparación de los datos y la transposición de bits en los resultados. Contando con esta problemática, un avance significativo ha sido la creación de MVDRAM, un sistema que permite la ejecución práctica y eficiente de GeMV en DRAM sin necesidad de modificar su estructura física.

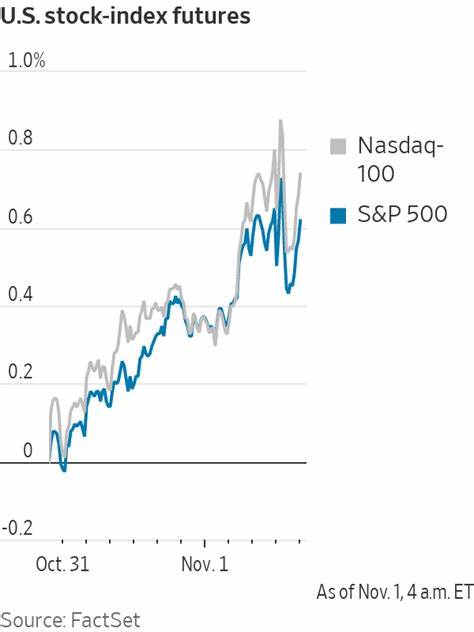

MVDRAM aprovecha patrones repetitivos en el intercambio de datos y la linealidad matemática inherente a la multiplicación matriz-vector para coordinar la cooperación entre procesador y memoria. Esta sinergia elimina las etapas costosas que solían afectar el rendimiento en implementaciones anteriores, haciendo posible un procesamiento de alta velocidad y bajo consumo en modelos de bajo bit, específicamente aquellos con cuantización inferior a 4 bits. Los resultados obtenidos mediante el uso de MVDRAM son sorprendentes. Experimentos realizados con módulos DDR4 convencionales han demostrado una aceleración de hasta 7.29 veces en las operaciones de GeMV cuando se comparan con implementaciones basadas exclusivamente en procesador.

Además, la eficiencia energética mejora en un factor de aproximadamente 30.5 veces, lo que representa un avance crucial para dispositivos móviles y sistemas embebidos que demandan operación prolongada sin recargas constantes. En el contexto de una inferencia completa en modelos LLM, MVDRAM incrementa el rendimiento hasta 2.18 veces para modelos de 2 bits y 1.31 veces para modelos de 4 bits, demostrando versatilidad y escalabilidad.

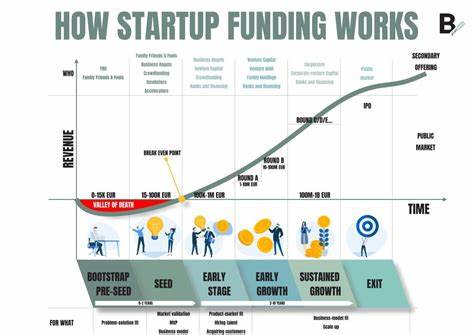

El impacto de estos avances va más allá de simples ganancias numéricas. Al habilitar la DRAM estándar como un acelerador para tareas intensivas en cómputo, se democratiza el acceso a hardware capaz de ejecutar inferencias LLM de forma eficiente, debilitando la barrera que representaban soluciones costosas y especializadas. Esto permite a consumidores y desarrolladores aprovechar capacidades de inteligencia artificial avanzada en dispositivos cotidianos, desde smartphones hasta laptops y sistemas IoT, sin necesidad de infraestructuras dedicadas. Además, MVDRAM sienta las bases para futuras investigaciones en la co-diseño de hardware y software, donde se puede imaginar un ecosistema de inteligencia artificial profundamente integrado en las memorias y procesadores estándar, optimizando cada ciclo de cómputo y minimizando el desperdicio energético asociado a la transferencia de datos. A su vez, esta evolución apoyará el despliegue comercial de soluciones de IA en ambientes con restricciones físicas y energéticas estrictas, tales como robótica en exteriores, dispositivos médicos portátiles y sistemas autónomos en el sector industrial.

En conclusión, la implementación práctica de multiplicación matriz-vector en DRAM sin modificaciones para acelerar modelos de lenguaje cuantificados a bajos bits representa un hito tecnológico de gran relevancia. Sistemas como MVDRAM no solo mejoran significativamente la velocidad y consumo energético en operaciones críticas, sino que también amplían la accesibilidad y capacidad de los dispositivos para integrar IA avanzada. Conforme la inteligencia artificial sigue expandiéndose en todos los ámbitos de la vida cotidiana, innovaciones como esta serán fundamentales para construir un futuro más inteligente, eficiente y conectado.