El desarrollo tecnológico ha ido buscando constantemente soluciones cada vez más eficientes para el procesamiento de datos, especialmente en áreas donde la rapidez y el bajo consumo energético son fundamentales. En este contexto, el diferenciador ferroeléctrico en memoria se presenta como una innovación disruptiva que permite realizar cálculos diferenciales directamente en el hardware de memoria, rompiendo las limitaciones tradicionales de los métodos digitales convencionales. Esta tecnología aprovecha las propiedades únicas de los materiales ferroeléctricos para ejecutar operaciones matemáticas complejas de manera analógica, facilitando aplicaciones desde la resolución de derivadas matemáticas hasta la extracción y detección de movimiento en imágenes. La importancia del cálculo diferencial es indiscutible en diversas disciplinas científicas y tecnológicas. Matemáticas, física, ciencias de la computación e ingeniería fundamentan parte de sus avances en la capacidad para calcular derivadas, las cuales permiten entender y predecir comportamientos dinámicos en sistemas variados.

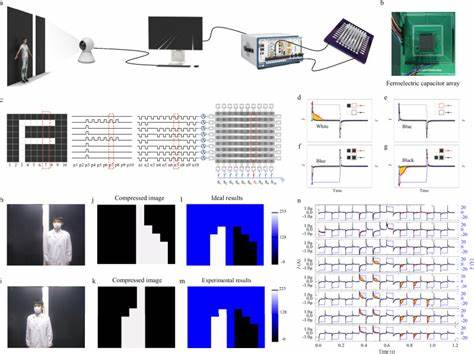

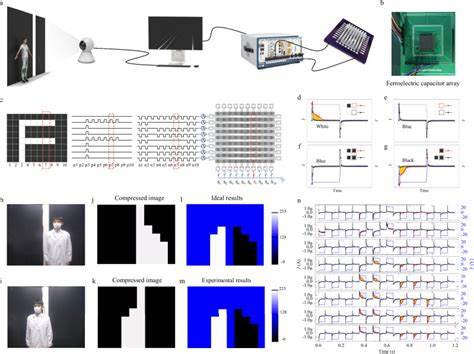

Sin embargo, la implementación digital clásica para realizar estas operaciones suele implicar procesos complejos que requieren acceso repetido a la memoria, transferencia de grandes volúmenes de datos y múltiples etapas de procesamiento, lo cual conlleva sobrecostos en tiempo y consumo energético, limitando su desempeño en sistemas de computación en el borde (edge computing) donde la eficiencia es prioritaria. Frente a esta problemática surge el concepto del diferenciador ferroeléctrico en memoria, el cual fusiona la capacidad de almacenamiento y el procesamiento diferencial en un único dispositivo. Este diferenciador está construido con una matriz cruzada de capacitores ferroeléctricos fabricados a partir de copolímeros orgánicos de P(VDF-TrFE), materiales reconocidos por su notable ferroelectricidad, estabilidad química y biocompatibilidad. La configuración de estos capacitores en un array pasivo 40x40 permite representar datos mediante la orientación de dominios ferroeléctricos que pueden ser direccionados por impulsos eléctricos programados con precisión. Esta estructura logra superar uno de los mayores desafíos en las matrices cruzadas pasivas, el llamado efecto sneak path, gracias a la dinámica no lineal y al estrecho margen de conmutación de sus dominios ferroeléctricos.

El proceso fundamental que permite al diferenciador ferroeléctrico operar es la inversión de los dominios de polarización inducida por campos eléctricos superiores al campo coercitivo. Al recibir una secuencia de pulsos con polaridades que codifican información digital o análoga, el sistema sólo altera el estado de aquellos dominios que representan un cambio entre la señal actual y la almacenada anteriormente. De esta forma, mediante la detección de las corrientes transitorias generadas durante la reversión de polarización, es posible identificar las diferencias directamente en la memoria sin necesidad de transmitir o almacenar redundancias de datos. Este mecanismo resulta ser una forma eficiente de cómputo analógico que realiza operaciones diferenciales en tiempo real mientras mantiene la información en estado no volátil. La demostración de esta capacidad se ha llevado a cabo mediante la resolución de derivadas de funciones matemáticas clásicas.

Por ejemplo, al codificar el valor de una función parabólica en la matriz de capacitores y al provocar la inversión secuencial de dominios de acuerdo con los valores de la función en varios puntos, se logra calcular tanto la derivada primera como la segunda con alta precisión. La linealidad entre la suma de las cargas producidas por los cambios en los dominios ferroeléctricos y la cantidad de unidades activadas asegura una representación analógica fiable del cálculo diferencial. Esto no sólo pruebas la factibilidad matemática sino que también sienta las bases para aplicaciones prácticas en la aceleración del procesamiento matemático mediante hardware especializado. Adicionalmente, el diferenciador ferroeléctrico en memoria muestra un gran potencial en tareas de procesamiento visual y análisis de imagen, particularmente en la extracción de movimiento y detección de discrepancias temporales entre fotogramas consecutivos o imágenes separadas por largos intervalos de tiempo. Inspirándose en la forma en que los sistemas biológicos procesan localmente la información visual, la tecnología humana emula este procesamiento desplazando la operación diferencial al nivel de la memoria que recibe la información del sensor de imagen.

Esto evita operaciones redundantes de lectura, escritura y cálculo en unidades de control central, logrando un ahorro sustancial de energía y tiempo de procesamiento. En la práctica, cada pixel de una imagen capturada por sensores CMOS es codificado y enviado a un capacitor ferroeléctrico específico en la matriz. Gracias a la no volatilidad de los dominios ferroeléctricos, sólo aquellos capacitores vinculados a pixels que han cambiado de estado entre imágenes consecutivas experimentan inversión de dominio y generan señales medibles. Esta propiedad permite que sólo los elementos con información relevante de cambio activen una respuesta, filtrando el ruido y reduciendo el procesamiento superfluo. Así, se consigue una representación directa y eficiente del movimiento o de las diferencias de imagen.

La operación del diferenciador a frecuencias de hasta 1 MHz garantiza que pueda procesar video y señales en tiempo real para aplicaciones avanzadas como reconocimiento de objetos en vigilancia, compresión de video y sistemas inteligentes de monitorización. Además, la robustez en la retención de información durante varios días permite su uso en escenarios donde las imágenes comparadas no son consecutivas en el tiempo, por ejemplo, para el monitoreo de defectos en manufactura o control de cambios en infraestructuras críticas. Uno de los aspectos técnicos clave en este diseño es la solución al problema de los caminos de fuga (sneak paths) característicos de las matrices cruzadas pasivas, que suelen originar errores de lectura y conmutación no deseada. En esta implementación, la naturaleza no lineal y el estrecho rango de conmutación de los dominios ferroeléctricos garantizan que sólo las celdas cuya tensión supera el umbral coercitivo experimentan cambio de estado, lo que otorga alta inmunidad a interferencias eléctricas externas y mejora la precisión del sistema. Además, la fabricación de la matriz con polímeros ferroeléctricos de P(VDF-TrFE) mediante procesos de solución y deposición controlada ofrece ventajas en costos y materiales, con films uniformes que muestran estructura cristalina adecuada para un rendimiento estable.

La capacidad de fabricar dispositivos con alta uniformidad y reproducibilidad, como lo indica el elevado rendimiento del 100% de celdas funcionales en las matrices probadas, abre la puerta a escalabilidad industrial. El bajo consumo energético es otra ventaja sobresaliente. Cada operación diferencial consume cantidades del orden de femtojoules, un nivel cientos de miles de veces inferior al consumo en métodos digitales tradicionales, posicionando a esta tecnología como ideal para dispositivos IoT y sistemas embebidos que exigen eficiencia y autonomía prolongada. Las perspectivas futuras sugieren que la integración de materiales ferroeléctricos de nueva generación, como los basados en hafnio, podría reducir aún más los voltajes de operación y aumentar la velocidad de conmutación a escalas sub-picosegundos, fortaleciendo la competitividad y las aplicaciones del diferenciador ferroeléctrico en memoria. Asimismo, la incorporación con circuitos periféricos especializados permitirá mejorar la linealidad del sistema y ampliar la representación analógica para cálculos más complejos.

En resumen, el diferenciador ferroeléctrico en memoria representa un avance significativo en la convergencia entre almacenamiento y procesamiento de datos, que rescata conceptos históricos como el motor diferencial de Charles Babbage y los adapta a las tecnologías modernas para cumplir con los retos de la computación actual. Su capacidad para realizar cálculo diferencial analógico, con eficiencia energética y velocidad sobresaliente, junto con su aplicación en procesamiento visual en tiempo real, abre una nueva era de hardware inteligente, prometiendo impactos en campos tan variados como inteligencia artificial, visión computarizada, sistemas embebidos y manufactura de semiconductor. El futuro de esta tecnología parece prometedor, y sin duda continuará siendo objeto de investigaciones y desarrollos que ampliarán sus capacidades y su integración en dispositivos cotidianos, acercando el procesamiento inteligente y eficiente a todos los niveles del ecosistema tecnológico.