En el ámbito del diseño de hardware, el término "síntesis" puede generar cierta confusión, particularmente cuando se habla de síntesis de alto nivel, conocida también como High-Level Synthesis (HLS). Entender la distinción clara entre los diferentes procesos de síntesis es fundamental para profesionales y estudiantes de ingeniería electrónica y de sistemas digitales que buscan optimizar sus diseños y mejorar la comunicación técnica en sus proyectos. La síntesis, en términos generales, se refiere al proceso mediante el cual un diseño abstracto es transformado en una representación más concreta, adecuada para su fabricación o implementación. Sin embargo, en el contexto del diseño digital moderno, existen diversas etapas y tipos de síntesis que cumplen funciones específicas dentro de un flujo de diseño integrado. La síntesis de alto nivel y la síntesis RTL (Register Transfer Level) representan dos de estos procesos clave, y diferenciarlas no solo ayuda a clarificar conceptos sino que también es esencial para documentar y comparar resultados de manera precisa.

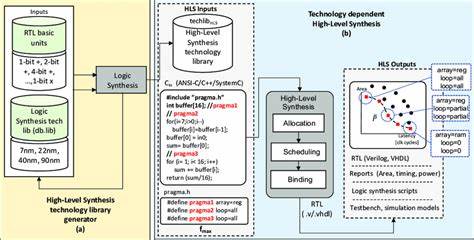

La síntesis de alto nivel o síntesis HLS es el proceso que toma un diseño descrito en lenguajes de programación de alto nivel como C o C++, y lo transforma en un código RTL o lenguaje de descripción de hardware (HDL) como VHDL o Verilog. Esta conversión incluye varias etapas importantes, como la compilación frontend, la programación de horarios (scheduling), la asignación o binding de recursos, y finalmente la generación de código HDL. Estas fases permiten que un diseño originalmente pensado para un software pueda traducirse en una lógica hardware tangible que luego será utilizada para la fabricación o simulación del circuito. En contraste, la síntesis RTL se encarga de tomar este código RTL y convertirlo en una estructura más cercana al hardware físico, como un netlist de puertas lógicas o en una descripción para herramientas de colocación y enrutamiento en un proceso para VLSI (Very Large Scale Integration). Este paso es crucial para evaluar parámetros como el área, consumo energético, latencia y velocidad del circuito implementado.

Muchas veces, quienes inician en esta área se enfrentan a la duda respecto a cómo nombrar el proceso dentro del flujo de diseño. Por ejemplo, cuando alguien menciona “después de la simulación C y la síntesis,” puede entenderse que se habla de la síntesis que ocurre dentro de herramientas HLS. Sin embargo, en contextos donde la comparación entre distintas síntesis es necesaria, simplemente usar “síntesis” genera ambigüedad. Por ello, es común y recomendable utilizar expresiones como “síntesis HLS” o “síntesis RTL” para ser más explícitos. A pesar de que frases como “síntesis de síntesis de alto nivel” pueden sonar redundantes, ayudan a la claridad, especialmente en artículos académicos y reportes técnicos.

La distinción también cobra importancia en investigación y desarrollo, donde es frecuente analizar el desempeño estimado tras la síntesis HLS y luego comparar el resultado final tras la síntesis RTL. Esta comparación permite identificar cuellos de botella, estimar la eficiencia real del diseño y aplicar técnicas de optimización más acertadas. Además, dentro del entorno o ecosistema de herramientas HLS, existen distintos “flujos” o etapas más allá de la síntesis, tales como la simulación C (csim), la simulación co-simulación RTL (cosim), el proceso de síntesis propiamente dicho y la exportación o empaquetado del hardware resultante para su integración en entornos más amplios. En este sentido, referirse a la etapa específica de conversión a RTL como “síntesis HLS” facilita la comunicación precisa y evita confusiones con los otros procesos que conforman el flujo. Por otro lado, es interesante reflexionar sobre los términos que rodean el diseño de hardware.

Palabras como “implementación,” “VLSI,” “EDA” (Electronic Design Automation), “HDL,” o “HLS” representan conceptos vinculados pero no equivalentes. Comprender sus alcances y límites contribuye a enriquecer la conversación técnica y académica. Asimismo, cuestiones aparentemente triviales como la pronunciación de acrónimos o el significado exacto de frases como “diseño de hardware” versus “diseño de chips” pueden influir en la claridad del mensaje y deben considerarse con cuidado. El avance constante en herramientas, lenguajes y metodologías relacionadas con la síntesis de alto nivel abre un campo de oportunidades para optimizar el diseño y la implementación de circuitos digitales cada vez más complejos y eficientes. La capacidad de transformar código escrito en lenguajes familiares como C++ en lógica de hardware funcional democratiza el desarrollo de sistemas embebidos y ASICs, haciendo accesible el diseño hardware a una base más amplia de profesionales.

En conclusión, la diferencia entre “síntesis HLS” y “síntesis RTL” es más que una cuestión terminológica: refleja la evolución del diseño digital desde etapas de alto nivel hasta la concreción física del dispositivo. Para quienes trabajan o estudian esta área, adoptar un lenguaje preciso contribuye a mejorar la documentación, el análisis y la innovación. Al hacerlo, también se facilita la colaboración interdisciplinaria y la transmisión efectiva del conocimiento dentro de las comunidades académicas y profesionales.