El mundo de las redes está en constante evolución y la necesidad de equipos accesibles, flexibles y de alto rendimiento es cada vez más crucial. En este contexto, el proyecto de switch Ethernet de hardware abierto representa un esfuerzo innovador que busca transformar la forma en que se diseñan y construyen los dispositivos de red, proporcionando una alternativa viable y documentada completamente abierta para la comunidad tecnológica. El origen de este proyecto se remonta a 2012, cuando comenzó el desarrollo de una primera generación de switch Ethernet de código abierto que, a pesar de no tener nombre definido y presentar varios desafíos, sirvió como fundamental para sentar las bases de una visión a largo plazo. En aquel entonces, la dificultad principal radicaba en la falta de ASICs para switches Gigabit con múltiples puertos que cumplieran los requisitos de un proyecto de hardware abierto: disponibilidad de especificaciones sin NDA, posibilidad de compra en cantidades unitarias y flexibilidad en diseño. Debido a estas restricciones, la elección lógica fue utilizar FPGAs y desarrollar desde cero una solución propia, lo que representó un reto considerable dada la experiencia inicial limitada y el equipamiento de prueba modesto.

Por ejemplo, el uso de líneas RGMII de 250 MT/s y la integración con PHYs RGMII exclusivamente fueron tecnologías punteras en ese momento, pero difícilmente verificables con osciloscopios básicos como el Rigol DS1102D de 100 MHz disponible. Aunque la primera versión no logró consolidarse totalmente, quedando uno de los PHYs sin funcionar adecuadamente y limitándose a tres puertos activos, el aprendizaje acumulado fue valioso. Se evidenció que la capacidad de la FPGA XC6SLX25 no era suficiente para integrar de forma cómoda el controlador DDR, un procesador softcore y las interfaces MAC requeridas, además del propio switching fabric. A su vez, la experiencia en diseño de señales de alta velocidad y la comprensión de las limitaciones del hardware inicial fueron factores claves para ajustar la estrategia futura. Durante los años siguientes, el desarrollador se enfocó en mejorar habilidades en diseño RTL, adquirir mejor equipamiento y crear herramientas para el ecosistema.

La adquisición de un osciloscopio LeCroy WaveSurfer de 350 MHz en 2015 fue un salto significativo que permitió avanzar en análisis de integridad de señal para RGMII y decodificación de protocolos Ethernet básicos. Sin embargo, el sueño era crear un equipo capaz de validar señales a 10 Gbps y más, lo cual impulsó el diseño del proyecto “FREESAMPLE”, una propuesta de osciloscopio de muestreo a 10 GHz que lamentablemente quedó inconclusa, pero que acercó aún más el conocimiento sobre pruebas de señales ultrarrápidas. Un hito destacado en este proceso fue el desarrollo paralelo de una sonda de 16 GHz completamente abierta, destinada a superar simultáneamente los retos de sondas y osciloscopios de alta frecuencia, pieza clave para validar señales de altísima velocidad que se esperan en switches modernos. Este avance evidenció la importancia de abordar integralmente tanto la instrumentación como el propio equipo de red. Asimismo, en el ámbito del software, el proyecto vio el renacer de herramientas para gestión y análisis de osciloscopio, evolucionando desde glscopeclient optimizado con OpenGL hasta ngscopeclient con aceleración Vulkan.

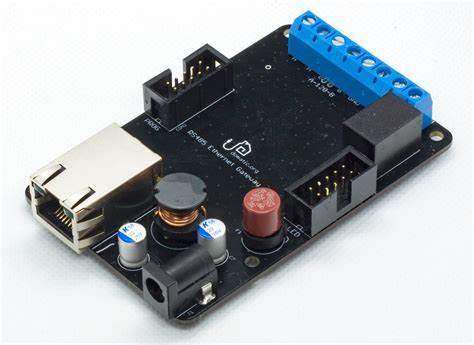

La integración de protocolos de red recientes y relevantes como 1000baseX, SGMII, QSGMII y 10Gbase-R complementaron el portafolio de capacidades para diagnóstico y desarrollo. Paralelamente, nació la idea de conformar una familia completa de equipos de red bajo el nombre de LATENTx, una denominación que utilizaba colores para identificar subproyectos y que recordaba por inspiración a denominaciones militares de sistemas experimentales. En este esquema, LATENTRED representaba un switch de borde Gigabit, mientras que LATENTORANGE apuntaba a un núcleo 10G, pero para materializar una plataforma de prototipado intermedia fue creado LATENTPINK. LATENTPINK fue un diseño ambicioso pensado para 14 puertos de 1G y una uplink SFP+ de 10G, utilizando un VSC8512 de 12 puertos con tecnología QSGMII que permitía una significativa reducción en pistas y pines requeridos, al comparar con el más tradicional SGMII o GMII. Esto fue importante para simplificar el diseño y mejorar la manejabilidad en PCB.

Además, se incorporaron microcontroladores STM32H7 y un FPGA para la lógica principal, siendo uno de los primeros diseños de 8 capas personales del autor. En esta iteración se destacó la implementación de una memoria externa QDR-II+ como buffer central en la arquitectura de conmutación, la creación de FIFOs asincrónicas por puerto y un sistema de forwarding basado en ronda entre puertos para balancear el tráfico. No obstante, algunos inconvenientes se presentaron, como errores en el bus de control centralizado, la limitación de un bus de datos con anchos de bits y velocidades variadas entre diferentes caminos y bugs en la disposición física del PCB que impactaron la conectividad de ciertos puertos. LATENTPINK logró demostrar la viabilidad de los conceptos y tecnologías usadas, estableciendo que se podía construir un switch funcional, capaz de procesar tramas, manejar VLANs de puerto y decodificar etiquetas 802.1q, aunque con capacidades limitadas en gestión avanzadas.

Esta experimentación le dio claridad de que el próximo desafío era desarrollar una plataforma mucho más robusta y escalable que enfrentara con mejores herramientas y FPGA más potentes los retos de rendimiento y funcionalidad. El siguiente objetivo fue LATENTRED, un switch pensado para un factor de forma 1U con dos tarjetas línea de 24 puertos cada una, utilizando dos VSC8512 por línea que sumaban 48 puertos Gigabit y enlaces ascendentes duales a 10 o 25 Gbps mediante SFP28. Esto partió de una cuidadosa evaluación del mercado para escoger módulos magjack apropiados y de una estrategia de interconexión con cables de alto desempeño, como los de la serie AcceleRate ARC6/ARF6 de Samtec, diseñados para manejar tasas de velocidad muy superiores a las requeridas, lo que facilita una implementación eficiente y práctica a nivel mecánico. Para alimentar este potente switch, LATENTRED contempla cinco o seis placas PCB diferentes, incluyendo conversores de bus intermediarios, distribución y monitorización de potencia, tarjetas línea con PHYs, y una placa principal de motor de conmutación que integra un FPGA Kintex UltraScale+ XCKU5P, así como microcontroladores STM32 para la gestión y monitores específicos. Esta configuración considera además la posibilidad de placas separadas para uplinks, buscando flexibilidad en diseño y fabricación.

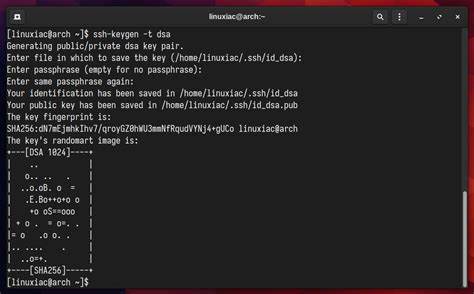

El hallazgo más relevante en esta etapa fue el descubrimiento y adquisición de FPGAs XCKU5P a precios muy bajos mediante proveedores alternativos, lo que desbloqueó capacidades de hardware excepcionales para el proyecto. Esta FPGA ofrece más LUTs, RAM block y la inclusión de UltraRAM optimizada para buffers masivos, así como hasta 16 transceptores rápidos de 28 Gbps, que permiten un desempeño muy por encima de generaciones anteriores usadas. Esta potencia adicional amplía considerablemente las opciones para el diseño del fabric de conmutación, permitiendo implementar un crossbar 4x4 de 64 bits a 400 MHz que puede manejar anchos de banda de más de 102 Gbps, con flexibilidad para diferentes configuraciones de enlace y procesamiento de tráfico, incluyendo multicasting y broadcast. Las soluciones en gateware y arquitectura interna están siendo refinadas para aprovechar estos recursos, integrando interfaces AXI4-Stream para MAC/PCS Ethernet a 10G y desarrollando los bloques necesarios para gestión de VLANs, comprobación de tramas y administración de direcciones MAC. En términos prácticos, el estado actual del hardware incluye el diseño finalizado y probado de tarjetas línea, distribución y alimentación, mientras que el motor principal del switch está en fase experimental con prototipos y versiones tempranas que permiten validar comunicaciones entre FPGA, tarjetas línea y controladores mediante enlaces seriales y buses personalizados, como el Serial Chip to Chip Bus.

La perspectiva para los próximos meses incluye la integración de las piezas restantes, testeo extensivo del fabric de conmutación, implementación completa del stack de protocolos y gestión, y eventualmente la producción en pequeña serie para validar las funcionalidades en entornos reales. Se prevé que la madurez del proyecto y los diseños físicos culminarán alrededor de 2026, aunque factores externos como cadena de suministro y condiciones geopolíticas pueden impactar los tiempos. En suma, el proyecto del switch Ethernet de hardware abierto representa un fascinante viaje tecnológico, desde intentos iniciales con equipos modestos hasta la materialización de un sistema complejo, robusto y escalable que puede contribuir de forma significativa a democratizar el acceso a tecnologías avanzadas de networking. La conjunción de hardware abierto, desarrollo de herramientas propias y una visión clara de escalabilidad posicionan este esfuerzo como un referente para iniciativas similares, demostrando que con perseverancia, innovación y adaptabilidad es posible potenciar el futuro de las redes abiertas y personalizadas.