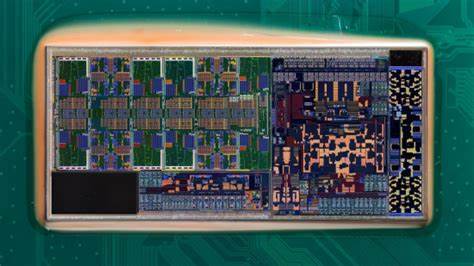

Intel ha presentado recientemente imágenes detalladas del die de su arquitectura Arrow Lake, que revelan importantes innovaciones en el diseño de sus procesadores, especialmente en el uso del enfoque basado en chiplets o mosaicos. Esta arquitectura, aunque no ha logrado destacarse en rendimiento en juegos, representa un avance tecnológico crucial para la compañía y un indicio claro de hacia dónde se dirige el futuro de sus CPUs de escritorio. El diseño de Arrow Lake se caracteriza principalmente por su estructura de múltiples chips o tiles integrados en un solo paquete. Este enfoque permite combinar tecnologías de proceso diferentes para optimizar funciones específicas del procesador, reducir costos y mejorar los rendimientos de fabricación. En las imágenes compartidas, se puede apreciar que el die está compuesto por varios mosaicos diferenciados: el tile de cómputo, el tile de entrada/salida (IO), el tile del sistema en chip (SoC) y el tile dedicado a la GPU, además de dos pequeñas piezas que actúan como refuerzos estructurales para aumentar la resistencia física del conjunto.

El tile de cómputo, que contiene los núcleos de procesamiento principales, es fabricado por TSMC usando su tecnología N3B, que es uno de los nodos más avanzados y pequeños disponibles en la actualidad. Esto asegura que los núcleos sean extremadamente eficientes en cuanto a rendimiento y consumo energético. En contraposición, los tiles que manejan IO y SoC son producidos mediante el proceso N6 de TSMC, un nodo más maduro, lo que ayuda a mantener a raya los costos sin sacrificar funcionalidad. Finalmente, todos estos componentes reposan sobre una base fabricada por Intel con tecnología FinFET de 22 nm, que actúa como soporte estructural y de interconexión para los chips más pequeños. Es importante destacar que Arrow Lake representa un cambio histórico para Intel, pues es la primera arquitectura de la compañía en la que la mayor parte de la fabricación recae en nodos de proceso de un competidor – en este caso, TSMC – una decisión estratégica que subraya la presión para continuar innovando y mantenerse competitivo en la industria de semiconductores.

En lo que respecta a la configuración interna de los núcleos, Intel optó después de varias iteraciones por un diseño híbrido novedoso: los núcleos de alto rendimiento (P-cores) están dispuestos de forma que rodean y abrazan a los núcleos de eficiencia (E-cores). Esta disposición pretende mejorar la gestión térmica al evitar que se concentren demasiados núcleos generadores de calor en un solo punto y, además, optimizar la comunicación entre ellos, a través de un sistema de interconexión desarrollado especialmente para esta arquitectura. Otro aspecto notable es la estrategia de caché empleada. Intel ha decidido equipar a cada núcleo P-core con 3 MB de caché L3, dando un total de 36 MB, mientras que los clusters de núcleos E-core comparten 3 MB de caché L2, segmentados en unidades de 1.5 MB para dos núcleos cada una, las cuales se interconectan entre sí y con la caché L3 de los P-cores.

Esta arquitectura de caché proporciona beneficios en la latencia y el acceso a datos, especialmente para los núcleos E, que por primera vez tienen acceso directo a la caché L3, un avance respecto a generaciones anteriores. Por supuesto, esta complejidad tiene un costo. Los primeros lanzamientos de Arrow Lake han mostrado limitaciones importantes en rendimiento, particularmente en juegos, debido a problemas latentes con la latencia de la interconexión de los chiplets. Esta latencia impacta la rapidez con la que los diferentes mosaicos intercambian información, ralentizando el desempeño general en aplicaciones sensibles al tiempo de respuesta. Intel está trabajando en resolver estos inconvenientes mediante actualizaciones de firmware y ajustes de diseño para futuras iteraciones.

La ventaja estratégica del diseño basado en chiplets es que permite a Intel desarrollar, optimizar y fabricar cada tile de manera independiente, utilizando distintas tecnologías de proceso según convenga. Esto no solo mejora el rendimiento y eficiencia de forma escalonada, sino que también reduce costos y permite una mejor gestión de la cadena de suministro. En el panorama competitivo, a pesar de que Arrow Lake no logra superar a los procesadores Ryzen 9000 de AMD en potencia para juegos ni mejora sustancialmente a la generación previa de Intel, marca un paso crucial para la empresa. Su diseño modular basado en chiplets plantea una base sólida para futuras arquitecturas más eficientes, potentes y económicas. La apuesta por los chiplets también abre la puerta a configuraciones personalizadas y a una evolución más acelerada, donde Intel puede actualizar o reemplazar solo algunas partes del procesador en lugar de tener que rediseñar un monolito completo.

Este modelo también se adapta mejor a las exigencias actuales del mercado, donde la flexibilidad y la capacidad de respuesta rápida son decisivas para el éxito. Además del impacto técnico, las imágenes del die de Arrow Lake han generado gran interés en la comunidad tecnológica, que analiza cada detalle buscando pistas sobre el rumbo de Intel. Este tipo de contenido no solo es esencial para comprender la evolución del hardware, sino que también promueve el debate y la expectativa en torno a la próxima generación de procesadores. En conclusión, Arrow Lake representa para Intel un experimento ambicioso y un punto de inflexión en su estrategia de desarrollo. Si bien enfrenta desafíos en el corto plazo, la migración a una arquitectura basada en chiplets es un movimiento acertado para mantenerse relevante en un mercado altamente competitivo y dinámico.

Con el tiempo y mejoras continuas, esta arquitectura podría sentar las bases para una nueva era de procesadores que combinan eficiencia, potencia y flexibilidad, respondiendo a las demandas cada vez más exigentes de usuarios y profesionales en todo el mundo. Intel probablemente seguirá explorando y optimizando esta vía, buscando alcanzar el equilibrio perfecto entre rendimiento y consumo, y adaptándose a las innovaciones tecnológicas y a los cambios en el ecosistema de hardware.